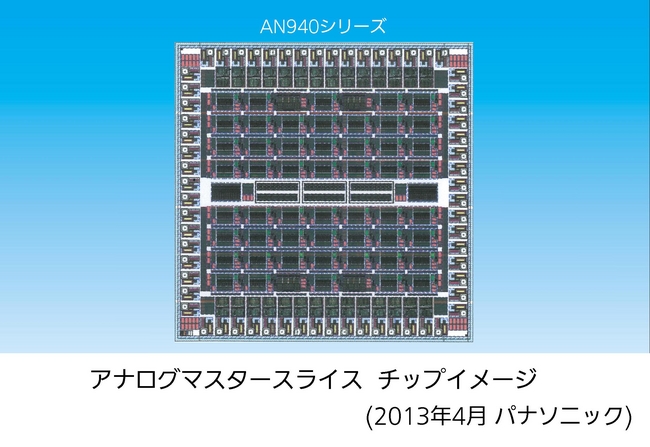

「アナログマスタースライス サービス」を開始

パナソニック株式会社 オートモーティブ&インダストリアルシステムズ社は、お客様のアナログカスタムIC開発をサポートする「アナログマスタースライス サービス」を開始します。

「アナログマスタースライス サービス」とは、予めバイポーラトランジスタ、抵抗、コンデンサ等をアレー状に配置したウェーハ上に、お客様が設計した回路を形成して、アナログカスタムICとしてご提供するサービスです。機器メーカーなどのお客様には、製品性能の差別化や保有技術、製品情報の秘匿、開発期間の短縮、機器の品質安定化などのため、カスタムICの回路設計を自社で行いたいという要望があります。当社はこのようなお客様のご要望にお応えするため、アナログカスタムICを高品質、高性能でありながら、設計を容易に短期間に低予算で開発できる「アナログマスタースライス サービス」のご提供を開始します。

<商品情報>

http://www.semicon.panasonic.co.jp/jp/products/analogmasterslice/

【生産数量の少ない産業・家電・車載・エネルギー関連機器に最適な「アナログマスタースライス サービス」の特長】

1.お客様の開発期間の短縮に貢献します

業界初※1の0.8um 14V コンプリメンタリ BiCMOS[1]プロセスを採用し、業界最多※1の素子を搭載。アナログカスタムICの柔軟な設計と部品点数の削減、回路設計期間の短縮に貢献します。

レイアウト設計完了から、最短2週間(標準3週間)でサンプルをご提供します。

2.お客様の回路の低消費電力化に貢献します

高周波特性の良いバイポーラトランジスタやデジタル回路を混載しており、高性能・高品質なアナログカスタムICの開発に貢献します。

3.3種類のプロセスデザインキットからお客様の現有の設計環境に合わせてお選びいただけます

プロセスデザインキット(PDK)[2]として、OrCAD/PSpice※2、Gateway※3、Virtuoso Analog Design Environment※4を準備しています。

4.少量の量産、試作のみの生産でもご利用いただけます

※1 2013年4月23日 当社調べ。バイポーラトランジスタを搭載するアナログマスタースライスとして。

※2 OrCADおよびPSpiceは、Cadence Design Systems, Inc.の米国およびその他の地域における登録商標です。 日本におけるOrCAD製品の販売、サポートは、サイバネットシステム株式会社が提供しています。

※3 Gatewayは米SILVACO社の製品で、株式会社シルバコ・ジャパンが取り扱っています。

※4 米Virtuoso Analog Design Environmentは、Cadence Design Systems, Inc.の製品で、日本ケイデンス・デザイン・システムズ社が取り扱っています。

【販売計画】

シリーズ名:AN940/AN950シリーズ

試作サービス開始:2013年4月

開発費および価格:個別相談

試作期間:レイアウト設計完了後、最短2週間(標準3週間)

月産数量/試作数量:1,000個~/60個~(試作のみも対応します)

【用途】

生産数量の少ない各種機器向けの小規模のアナログカスタムIC

▼本件に関するお問合せ先

●報道関係お問合せ先

オートモーティブ&インダストリアルシステムズ社 広報グループ

TEL:06-6904-4732

●商品に関するお問合せ先

http://panasonic.co.jp/ais/contact/

●パナソニック株式会社 オートモーティブ&インダストリアルシステムズ社 ホームページ

http://panasonic.co.jp/ais/

<商品情報>

http://www.semicon.panasonic.co.jp/jp/products/analogmasterslice/

----------------

【開発フロー概略】

お客様による回路設計を基本としますが、回路設計から、試作、組立、検査まで充実のサポート体制を持ち、仕様設計、回路設計(図1 Case1)、レイアウト設計(図1 Case2)、テスト設計(図1 Case3)など、どの工程からでも後工程の開発を当社にご指示いただけます。

【特長の説明】

1.お客様の開発期間の短縮に貢献します

バイポーラトランジスタを搭載するアナログマスタースライスとして、業界初※1の0.8umデザインルールを採用し、業界最多※1の搭載素子数を備えています。配線工程前の素子形成までの工程を完了したウェーハを準備し、お客様が設計した回路を配線層のみのマスクで実現するため、パッケージングされたサンプルをレイアウト設計後から標準3週間でお届けし、最短2週間で試作できる特急サービスも準備しています。また、レイアウト設計後から最短20週間で量産開始が可能です。

2.お客様の回路の低消費電力化に貢献します

PNP型とNPN型トランジスタの周波数特性がほぼ同一のコンプリメンタリBiCMOSを採用することにより、トランジスタの高速駆動が可能になるため、回路の低消費電力化が可能です。用途に応じて、(1)アナログ専用版(2)ゲートアレー混載版の2種を2013年4月より受注開始します。アナログ専用版においても、CMOS入力のオペアンプが設計できるモジュールや簡単な論理ゲートを搭載しており、デジタル回路を混載することが可能です。ゲートアレー混載版では、数100ゲートのデジタル回路の混載が可能です。

3.3種類のプロセスデザインキットからお客様の現有の設計環境に合わせてお選びいただけます

回路設計環境として、業界でよく利用されている3種類の設計ツールのPDKをご提供します。

(1)OrCAD/PSpice※2 (回路設計環境のみ)

(2)Gateway※3 (回路およびレイアウト設計環境)

(3)Virtuoso Analog Design Environment※4 (回路およびレイアウト設計環境)

4.少量の量産、試作のみの生産でもご利用いただけます

月産1,000個の小ロットの量産からご利用いただけます。また、動作検証用などとして量産のない試作のみもご利用いただけます。

【用語説明】

[1]コンプリメンタリBiCMOS

ほぼ同一の特性のPNP型とNPN型のバイポーラトランジスタと、CMOSトランジスタを混載する半導体プロセス。

[2]プロセスデザインキット(PDK)

設計ツールに必要な、半導体プロセスデータ、ドキュメントの総称。SPICEモデルパラメータや回路図をEDAツールに入力するための回路図シンボル、マスクレイアウトに必要な情報、デザインガイド等のドキュメントを指す。

[3]遮断周波数

正確には電流利得遮断周波数と呼び、ftと表現する。トランジスタの電流利得が1倍(0dB)となる、周波数を指す。トランジスタが発振可能な最大発振周波数fmaxとともに、トランジスタの高周波性能を表す重要な指標である。

<商品情報>

http://www.semicon.panasonic.co.jp/jp/products/analogmasterslice/

すべての画像